인텔 Agilex 7 FPGA® 범용 I/O 및 LVDS SERDES 사용자 가이드 의 핀 배치 요구 사항에 따라 각 x4 DQ 그룹은 동일한 OE, 재설정 및 클럭 활성화 신호를 공유하므로 x4 DQ 그룹 내에서 OE, 재설정 또는 클럭 활성화 신호를 분할할 수 없습니다. 제약 조건을 감안할 때 I2C 핀을 배치할 때 몇 가지 고려 사항이 있습니다.

1. FPGA 멀티 마스터 모드가 필요한 I2C 마스터로 사용됩니다.

(i) I2C의 일반적인 구현은 아래와 같이 SCL과 SDA 모두에서 OE를 사용하고 있습니다. 따라서 동일한 x4 DQ 그룹에 SCL 및 SDA를 배치할 수 없습니다.

할당 i2c_serial_scl_in = arduino_adc_scl;

할당 arduino_adc_scl = i2c_serial_scl_oe? 1'b0: 1'bz;

할당 i2c_serial_sda_in = arduino_adc_sda;

할당 arduino_adc_sda = i2c_serial_sda_oe? 1'b0: 1'bz;

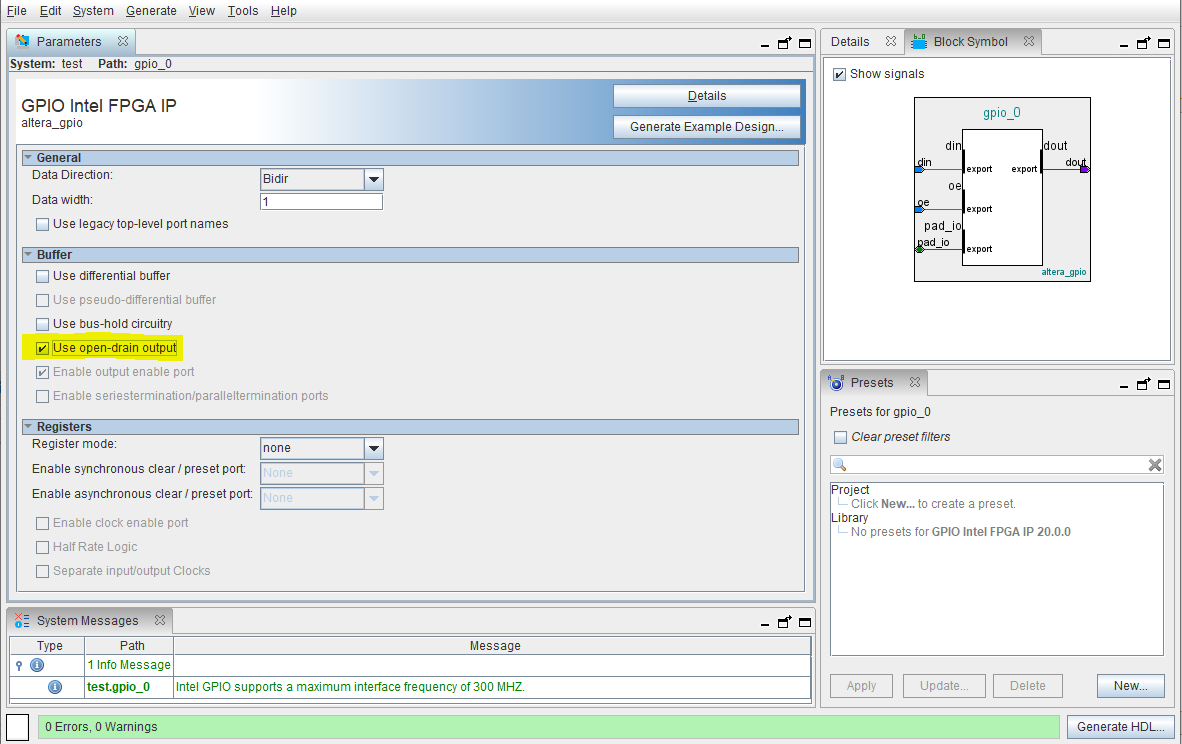

(ii) 또 다른 방법은 GPIO 인텔 FPGA IP 사용하는 것입니다. SCL 및 SDA의 오픈 드레인을 활성화하고, SCL 및 SDA용 OE 포트를 모두 1(높음)에 연결하고, 원래 OE 제어 신호의 반전 신호를 연결할 수 있습니다. 이러한 방식으로 제약 조건을 해결해 볼 수 있습니다. 다음은 예입니다.

gpioip gpioip_scl(

.dout(i2c_serial_scl_in),

.din(~i2c_serial_scl_oe),

.oe(1'b1),

.pad_io(arduino_adc_scl)

);

gpioip gpioip_sda (

.dout(i2c_serial_sda_in),

.din(~i2c_serial_sda_oe),

.oe(1'b1),

.pad_io(arduino_adc_sda)

);

2. FPGA I2C 마스터 단일 모드로 사용됩니다.

SCL은 OE가 없는 출력 핀입니다. SDA는 OE를 탑재한 양방향 핀입니다.

3. FPGA I2C 슬레이브로 사용됩니다.

SCL은 OE가 없는 입력 핀입니다. SDA는 OE를 탑재한 양방향 핀입니다.

위의 2 및 3에서는 SCL에 OE가 없기 때문에

- 동일한 x4 DQ 그룹에 SCL 및 SDA를 할당할 수 있습니다.

- 동일한 x4 DQ 그룹에 여러 SCL 및 SDA를 할당할 수 있습니다.

- 동일한 x4 DQ 그룹에 여러 SDA를 할당할 수 없습니다.

- 동일한 x4 DQ 그룹에 여러 SDA가 할당되면 위에서 언급한 GPIO 인텔 FPGA IP 사용하는 것도 해결 방법입니다.