이 오류는 내보낸 도관과 함께 일반 직렬 플래시 인터페이스 인텔® FPGA IP 디자인을 포함하는 모든 인텔 Agilex® 장치 대상 디자인을 컴파일하는 동안 인텔® Quartus® Prime Pro Edition 소프트웨어에서 나타날 수 있습니다. 설계 핀 배치에 출력 활성화(OE) 충돌이 있기 때문입니다. 여러 OE 충돌이 감지되는 경우 다른 핀 할당에서 오류가 중복될 수 있습니다.

모든 인텔 Agilex 장치에서 OE 하드웨어가 x4 DQ 그룹 핀 간에 공유되어 있기 때문에 핀 배치 요구 사항이 있습니다. 따라서 각각의 OE 신호를 갖는 두 개의 도관이 있는 경우 OE 충돌을 방지하기 위해 다른 x4 DQ 그룹 핀에 할당되어야 합니다.

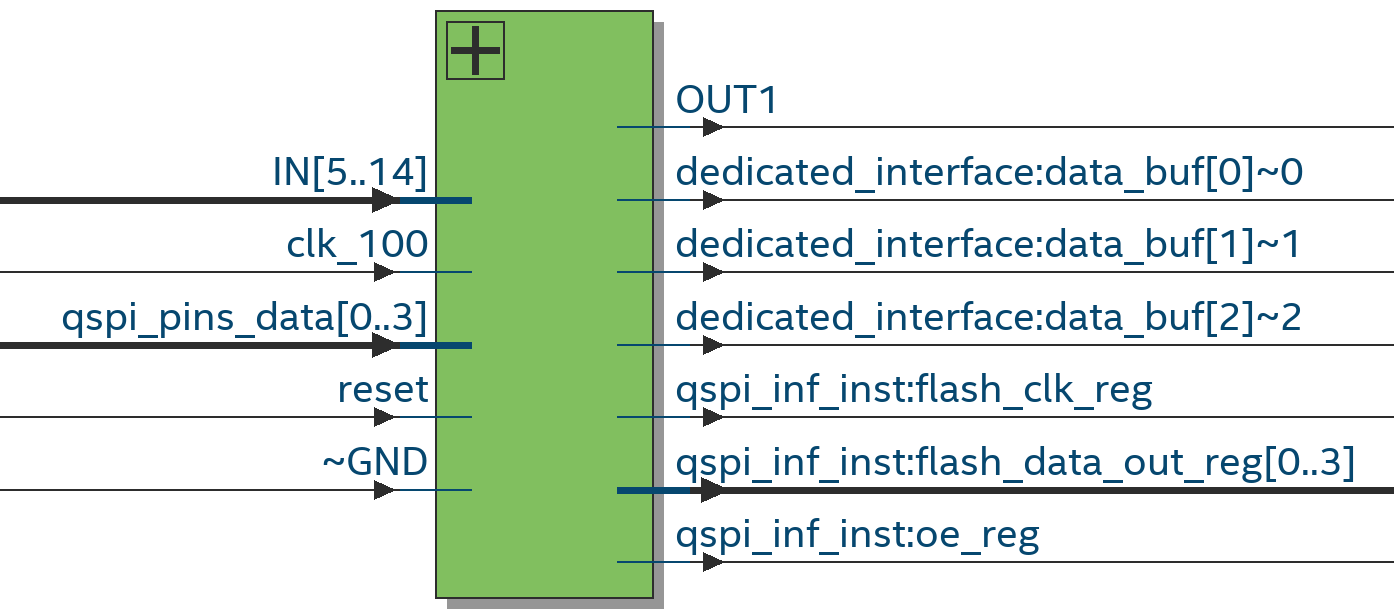

일반 직렬 플래시 인터페이스 인텔 FPGA IP(기술 맵 뷰어에서 보기)

| OE 신호 | 내보낸 도관 |

|---|---|

| dedicated_interface:data_buf[0]~0 | qspi_pins_data[0] |

| dedicated_interface:data_buf[1]~1 | qspi_pins_data[1] |

| dedicated_interface:data_buf[2]~2 | qspi_pins_data[2] qspi_pins_data[3] |

| qspi_inf_inst:oe_reg | qspi_pins_dclk qspi_pins_ncs |

이 오류를 방지하려면 다른 x4 DQ 그룹에 다른 OE 신호가 있는 내보낸 도관이 설정되어야 하는 반면, 공유 OE 신호가 있는 내보낸 도관은 동일한 x4 DQ 그룹 내에 설치하는 것이 좋습니다. 인텔 Agilex® 장치(AGFB027)를 사용하는 예는 다음 표에 표시됩니다.

| 내보낸 도관 | 핀 배치 | x4 DQ 그룹(AGFB027) |

|---|---|---|

| qspi_pins_data[0] | W34 | DQ133 |

| qspi_pins_data[1] | J35 | DQ135 |

| qspi_pins_data[2] qspi_pins_data[3] | L38 W38 | DQ132 |

| qspi_pins_dclk qspi_pins_ncs | J39 C38 | DQ134 |

이 정보는 인텔® Agilex™ 범용 I/O 및 LVDS SERDES 사용자 가이드 및 인텔 FPGA 핀아웃 파일 에서 확인할 수 있습니다.