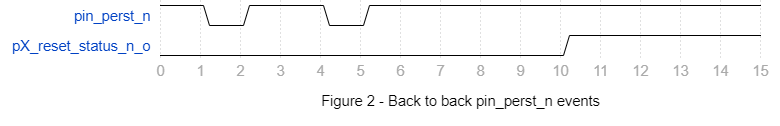

PCI Express 용 R-Tile Avalon® 스트리밍 인텔® FPGA IP pX_reset_status_n_o 신호에는 백투백 pin_perst_n 어설션 수와 관련된 누적 특성 이 포함됩니다.

각 백 투 백 pin_perst_n 이벤트는 하나씩 큐에 대기하고 실행되며, PCI Express의 R-Tile Avalon® 스트리밍 인텔® FPGA IP 리셋에서 나와 pX_reset_status_n_o 신호를 해제하는 데 걸리는 총 시간에 영향을 미칩니다.

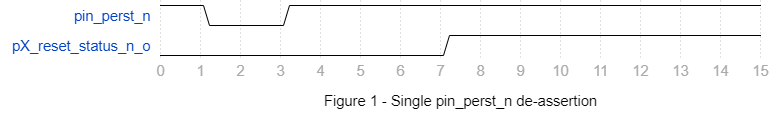

그림 1은 호스트에서 단일 pin_perst_n 어설션이 발행된 경우 PCI Express 동작에 대한 R-Tile Avalon® 스트리밍 인텔® FPGA IP 보여줍니다. 그림 2는 여러 pin_perst_n 어설션이 발행되는 경우 누적 특성을 보여줍니다.

PCI Express 사용자 가이드용 R-Tile Avalon® 스트리밍 인텔® FPGA IP 버전 22.2부터 이 정보를 포함하도록 업데이트되었습니다.