적절한 JTAG 타이밍 제약이 없기 때문에 여러 타일에 채널이 있는 설계를 로드할 때 인텔® 트랜시버 툴킷에 "채널 TX/RX/LINK|*에 대한 설정을 가져올 수 없습니다"라는 오류가 표시될 수 있습니다.

네이티브 PHY 소프트 로직의 배치로 인해 이러한 문제는 서로 다른 타일에 여러 네이티브 PHY 인스턴스화가 있을 때 가장 일반적으로 관찰됩니다.

해결 방법은 네이티브 PHY의 재구성 포트에 공급되는 재구성 클럭을 제한하는 것입니다. 그런 다음 'altera_reserved_tck'와 네이티브 PHY의 재구성 클럭 포트 'rcfg_clk'에 연결된 클럭이 모두 적절하게 제한되고 TimeQuest 내에서 타이밍을 통과했는지 확인합니다.

이 클록은 트랜시버 툴킷이 트랜시버의 CSR 공간에 액세스하는 데 사용하는 ADME(Altera Debug Mater Endpoint) 로직에 사용됩니다. SDC 명령 'create_clock'을 통해 설계에 선언된 다른 클럭이 하나 이상 있는 경우 사용자를 대신하여 자동으로 제한됩니다.

JTAG가 자동으로 제한되었는지 확인하려면 quartus_fit 출력에서 다음 메시지를 확인합니다.

"JTAG 신호에 기본 타이밍 제약 추가. 사용자가 그러한 제약을 제공하지 않았기 때문에 기본 기능을 달성하는 데 도움이 될 것입니다."

또는 더 정확하고 JTAG 클록을 수동으로 제한할 수 있습니다. 이를 위해 Quartus는 SDC 타이밍 템플릿을 제공했습니다.

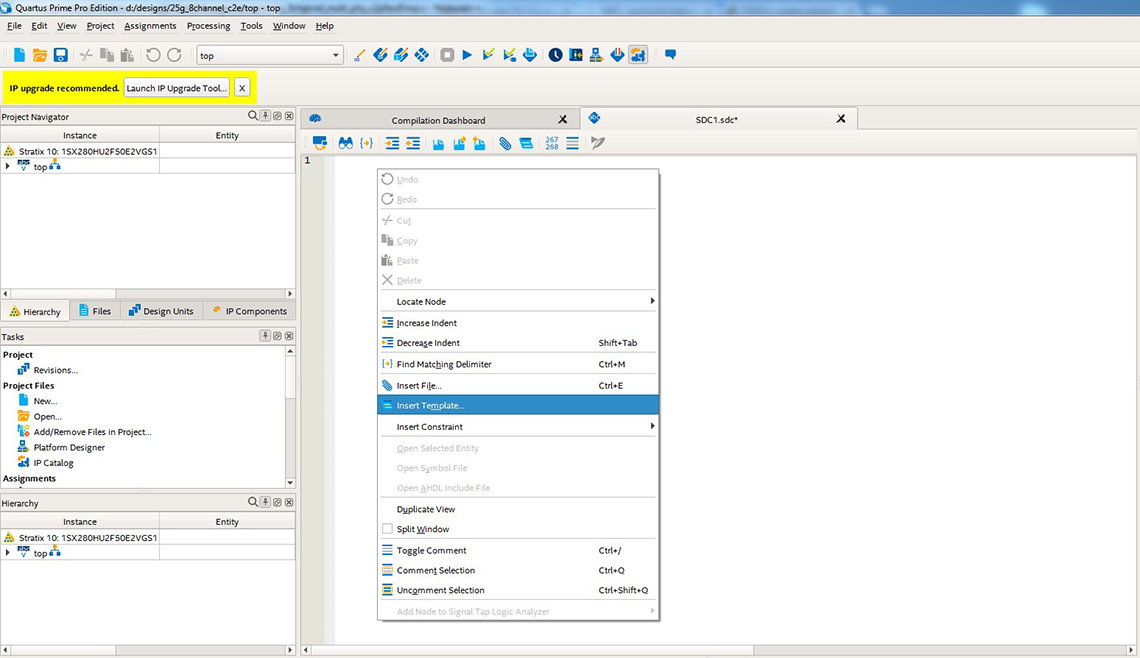

- Quartus Prime Pro Edition으로 SDC 파일 열기( 파일 -> 열기 )

- SDC 파일 창에서 마우스 오른쪽 버튼을 클릭하여 메뉴를 팝업합니다.

- '템플릿 삽입'을 선택합니다.

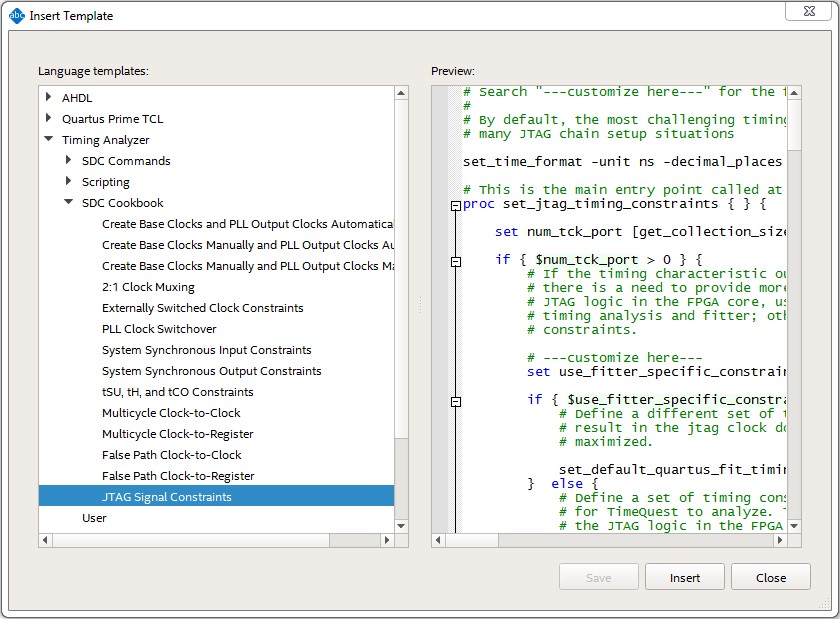

(4). 'JTAG Signal Constraint'를 선택하여 SDC 파일에 제약 조건을 삽입합니다.